## Design analoger Schaltkreise Übung zu Vorlesungen 6/7

10. Januar

## Aufgaben (Teil 1)

- Teil 1 sind Einführungsaufgaben

- Teil 2 sind praktische Aufgaben mit komplexeren Schaltungen

- Vorbereitung

- Erzeugen wir einen leeren Schaltplan (File, New Cellview, Schematic)

- Diesen Schaltplan können wir für alle Aufgaben verwenden

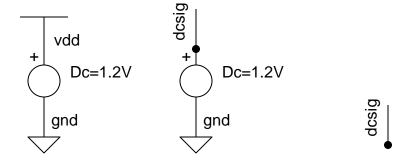

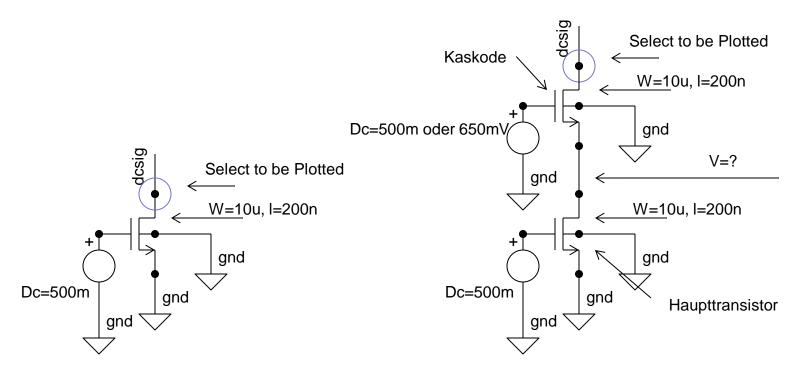

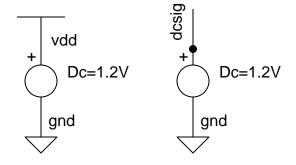

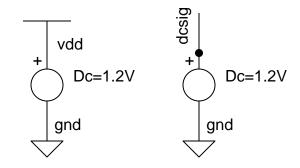

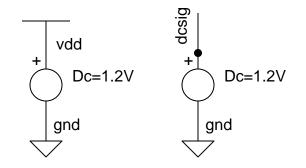

- Fügen wir folgende Objekte (Instanzen) ein: globale Spannungsquellen gnd, vdd, zwei dc Spannungsquelle vdc (Library analogLib).

- Schließen wir eine dc Quelle zwischen den gnd und vdd Objekten, so dass vdd = 1.2V (s. Abbildung nächste Folie)

- Kommentar 1: Wir schreiben nie Einheiten im Cadence so schreiben wir 100m und nicht 100mV

- Kommentar 2: Wir verwenden UMC 65nm Technologie, die 1.2V Versorgungsspannung hat.

- Schließen wir minus Pol der zweiten Quelle an gnd und puls Pol an einen Draht (wire) an.

- Benennen wir den Draht "dcsig". Setzen wir den "DC Voltage" Wert dieser Quelle auch 1.2

- Wir verwenden die Kopien vom "dcsig" Wire überall wo wir ein "dc Signal" brauchen, z.B. für die Simulationen von DC-Kennlinien

• ..

- Aufgabe1: Transistor-Kennlinie

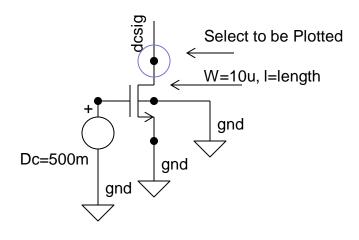

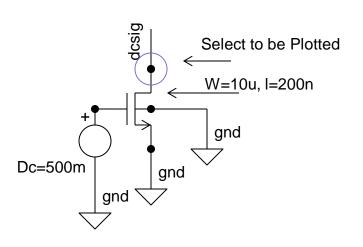

- Machen wir eine Instanz vom Transistor N\_12\_LLRVT (Library: umc65ll)

- Das ist der Standardtransistor in UMC 65 Technologie

- Schließen wir eine DC-Spannungsquelle von 500mV an Gate und eine Kopie vom Draht "dcsig"an Drain an (s. Abbildung nächste Folie)

- Wählen wir für den Transistor W=10um und L = length (Parameter)

- Simulieren wir die Ausgangskennlinie (lds = f(Vds)) auf die folgende Weise:

- Öffnen wir den Analogsimulator ADEL

- Wählen wir die Analyse dc

- Selektieren wir die DC Quelle mit "dcsig". Variieren wir (sweep variable) das Component Parameter "dc" im Bereich 0 bis 1.2(V). Wählen wir Sweep Type Linear mit dem Schritt 1m um die Genauigkeit zu erhöhen.

- Klicken wir zusätzlich "Save DC Operating Point"

- Selektieren wir unter "Outputs" -> "To be Plotted" -> "Select on Design, den Transistor-Drainstrom.

- (Wir klicken auf den Rechteckigen Drain-Kontakt siehe nächste Folie)

- (Alternativ kann man "Results->Direct Plot" benutzen)

- Setzen wir unter Design Variables length auf 200n

- Simulieren wir den Drain-Strom

- Machen wir eine Parametrische Analyse "Tools" "Parametric Analysis" für Parameter *length* im Bereich 60n bis 510n in etwa 5 Schritten.

- Aufgabe: Machen wir ein Screenshot vom Ergebnis

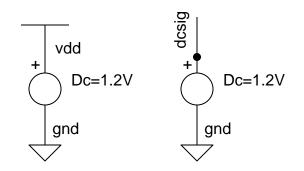

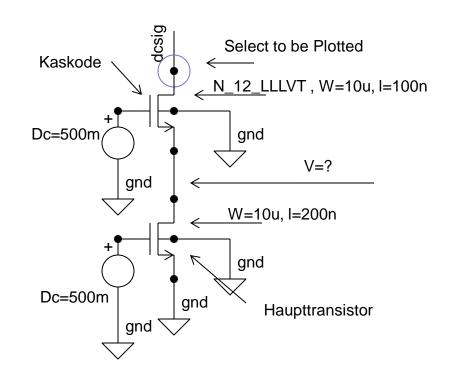

- Aufgabe 2: Transistor mit Kaskode

- Legen wir eine sinnvolle Länge L = 200n fest

- Kopieren wir den Transistor mit der Spannungsquelle am Gate und erweitern wir die Schaltung durch eine Kaskode (s. Abbildung auf der nächsten Seite)

- (Beachten wir beim Kopieren dass wir keine identische Wire-Labels in Original und der Kopie aus Versehen haben, sonst wären die Leitungen verbunden.)

- Wählen wir für die Kaskoden-Gatespannung zuerst 500mV (Gleich wie die Gate-Spannung des Haupttransistors)

- Simulieren wir den Drain-Strom von Kaskode als Funktion von Drain-Spannung, zusammen mir dem Drain-Storm des Einzeltransistors

- Plotten wir als Vergleich den Drain-Strom der Kaskode und des Einzeltransistors und speichern ein Screenshot. Sind die Ströme in Sättigung ähnlich?

- Wir können auf dem Schaltplan die DC Spannungen anzeigen lassen

- Für alle Spannungsquellen nimmt der Simulator die "DC-Voltage" Werte (Für "dcsig" Quelle ist es

1.2V)

- Schauen wir uns die Gate und Drain-Spannung des Haupttransistors an.

- Wir können für N/P\_12\_LLRVT Transistoren eine Schwelle-Spannung von 400mV annehmen

- Erinnern wir uns: Vdsssat = Vgs Vth

- Frage: Ist der Haupttransistor in Sättigung?

- Erhöhen wir das Gate-Potential der Kaskode um 150mV, und simulieren wir den Drain-Strom.

- Ist der Haupttransistor in Sättigung für "dcsig" = 1.2?

- Aufgabe: Plotten wir als Vergleich den Drain-Strom der Kaskode und des Einzeltransistors und speichern ein Screenshot. (Vergleichen wir rds)

- Aufgabe 3: Transistor mit einfacher Kaskode

- Ein Nachteil der Kaskode ist es, dass wir zwei verschiedene Spannungen für die Gates brauchen.

- Nehmen wir für die Kaskode den Transistor mit niedrigerer Schwelle N\_12\_LLLVT (Vth ~ 300mV)

und ändern wir die Länge von 200n auf 100n. Verwenden wir die gleiche Gate-Spannung von

500mV für die Kaskode und den Haupttransistor.

- Vergleichen wir die Kennlinien des Einzeltransistors und der Kaskode.

- Frage: Welche Kennlinie steigt weniger in Sättigung?

•

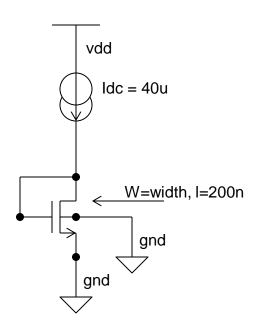

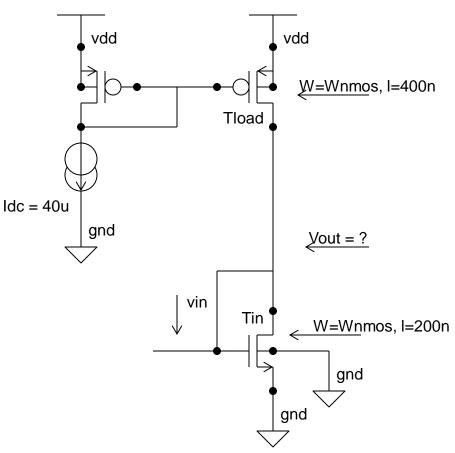

- Aufgabe 4: Dimensionierung des Eingangstransistors

- Aufgabe: Finden wir W des NMOS Transistors so, dass Vdssat des Transistor für einen Bias-Strom von 40uA etwa 100mV beträgt

- Zeichen wir die Schaltung wie in der nächsten Abbildung im gleichen Schaltplan

- Die Technologie UMC 65nm erlaubt eine maximale Breite des Transistors von nur 10um. Wenn wir stärkere Transistoren brauchen, müssen wir die Transistoren mit mehreren Gates benutzen. Setzen wir deshalb die Zahl von "Fingern"auf 2

- Definieren wir W als Parameter width, setzen wir L=200n

- Machen wir die parametrische Analyse f

ür width = 1u 20u, zahl der Schritten etwa 20.

- Polten wir die Gate/Drain Spannung als Funktion von width auf die folgende Weise:

- Verwenden wir dafür Analog Simulator -> "Tools" "Calculator"

- Mit diesem Tool kann man die Simulationsergebnisse auf verschiedenste Weise bearbeiten

- Klicken wir im Tool den Menu-Punkt vdc und selektieren Gate/Drain Draht auf dem Schaltplan

- Klicken wir Evaluate the Buffer

- Aufgabe: für welche Breite W haben wir Vdssat von etwa 100mV? (Vth = 400mV)

- Kommentar: Plotten wir Vgs es gilt Vdssat = Vgs Vth

- Man kann im Calculator auch die Transistorparameter wie gm oder rds berechnen

- Dafür muss man den Menu-Punkt "op" klicken, den Transistor selektieren und "gm" im Dropdown Menu finden

- Aufgabe: Plotten wir gm als Funktion von width

- **Frage:** Wie groß ist gm für *width* = 10u?

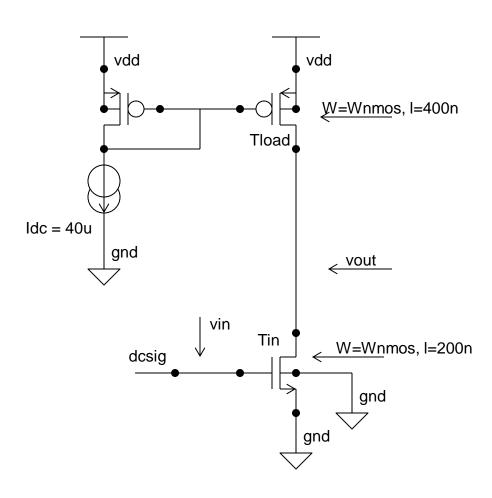

- Aufgabe 5: Verstärker mit PMOS Stromquelle Kennlinie

- Entwerfen wir den Verstärker mit einer PMOS Stromquelle wie in Abbildung

- Für NMOS nehmen wir L=200nm und W aus der vorherigen Aufgabe (Es soll gelten: Vdssat ~ 100mV für Ibias = 40uA)

- Dimensionieren wir den PMOS Stromspiegel

- Fangen wir mit Vdssat an. Wir "erlauben" dem PMOS etwa 2x mehr Vdssat als dem NMOS vdssat\_pmos = 200mV

- Laut Theorie gilt folgendes:

- Beim PMOS ist die Mobilität mu ist etwa 2x niedriger als beim NMOS, Cox ist gleich

- Vdssat = sqrt(Ibias \* L/W / mu Cox)

- Wenn wir Lpmos = 2 x Lnmos und W\_pmos = W\_nmos w\u00e4hlen bekommen wir gew\u00fcnschte Vdssat\_pmos = 2\* Vdssat\_nmos

- Setzten wir also: W\_pmos = W\_nmos und L\_pmos = 400n

- Aufgabe: Simulieren wir die DC-Kennlinie und machen ein Schreenshot ("dcsig" schließen wir an Gate vom Tin und plotten den Verstärker-Ausgang Vout)

- Frage: In welchem Ausgangs-Spannungsreich erwarten wir eine höhe Verstärkung (Im welchen Spannungsbereich am Ausgang sind Tload und Tin in Sättigung)

- **Frage:** Wie groß ist die maximale Spannungsverstärkung ungefähr. Bestimmen wir es graphisch aus dem Plot um den Punkt vout ~ vin ~ 500mV.

Schaltung für die Simulation von DC Kennlinie

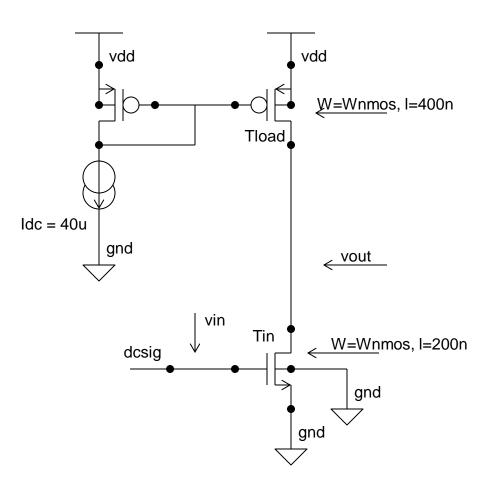

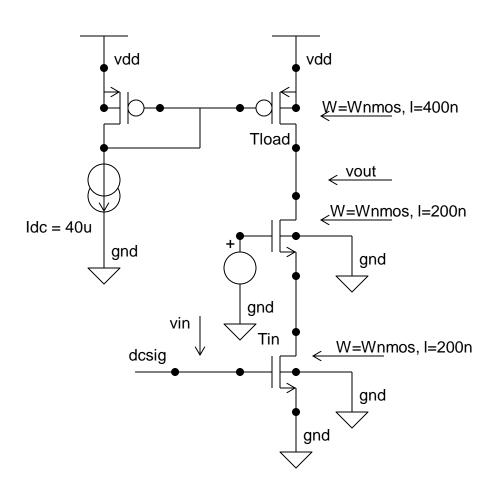

- Aufgabe 6: Verstärker mit PMOS Stromquelle Arbeitspunkt

- Wie in Vorlesungen erwähnt wurde, werden solche Verstärker nur mit Gegenkopplung verwendet.

- Normalerweise sorgt die Gegenkopplung, dass im Arbeitspunkt Vin = Vout ohne Signal gilt

- Machen wir eine Kopie des Verstärkers, entfernen wir Draht "dcsig" vom Eingang und schließen wir Vout und Vin kurz (s. Bild)

- Diese Hilfsschaltung hat den gleichen Arbeitspunkt wie wir später im Betrieb haben werden

- Wir werden solche Hilfsschaltungen benutzen um den Arbeitspunkt von Verstärkern zu untersuchen. (z.B. den Arbeitspunkt am Ausgang)

- Machen wir eine Simulation (Wir brauchen nur eine einzelne "Save DC Operating Point" Analyse, wir können aber Sweep "dcsig" aktiv lassen, da es nicht zu viel zeit nimmt)

- Verwenden wir das Tool: Results: -> Anotate -> DC Node Votages

- Frage: Wie groß ist DC Potential am Ausgang (Vout)?

- **Frage:** Um wie viel darf die Spannung am Ausgang steigen, bzw sinken, so dass die Transistoren in Sättigung bleiben?

- Verwenden wir Tool "Calculator" um gm und gds = 1/rds zu bestimmen

- Wir klicken "op", selektieren den Transistor und wählen "gm" oder "gds" im Dropdown Menu

- **Frage:** Wie groß sind die gm, gds vom Eingangstransistor Tin? Wie groß ist gds von Stromquelle Tload?

- Frage: Wie groß sollte die Verstärkung laut Theorie sein? (A = gm\_in (rds\_in || rds\_load))

- Stimmt es mit der Steigung der Kennlinie um den Punkt (Vout = 500mV) etwa überein?

•

Schaltung für die Simulation von DC Kennlinie

Hilfsschaltung für die Bestimmung des Arbeitspunktes

- Aufgabe 7: Kopieren wir den Verstärker aus der Aufgabe 5 und erweitern wir ihn durch eine NMOS Kaskode (s. Abbildung)

- Die Kaskode soll möglichst große gm haben, damit die sich ihre Gate-Source Spannung so wenig wie möglich ändert.

- Wählen wir die gleiche Dimensionen für die Kaskode wie für den Eingangstransistor

- Wählen wir die Gate-Spannung der Kaskode so, dass die Drain-Spannung des Eingangstransistors im Arbeitspunkt etwa 125mV ist. Benutzen wir für die Dimensionierung die Hilfsschaltung mit kurzgeschlossenem Eingang aus der Aufgabe 6.

- Für die optimale Kaskoden-Gatespannung gilt: Vgate = Vdssat\_in + Vdssat\_casc + Vth\_casc

- Beachten wir, dass das Substrateffekt die Schwelle-Spannung der Kaskode um etwa 25mV vergrößert

- **Aufgabe:** Simulieren wir die DC-Kennlinien des Verstärkers aus Aufgabe 5 und des Verstärkers mit Kaskode und machen ein Schreenshot ("dcsig" schließen wir an Gate vom Tin und plotten den Verstärker-Ausgang Vout)

## Aufgaben (Teil 2)

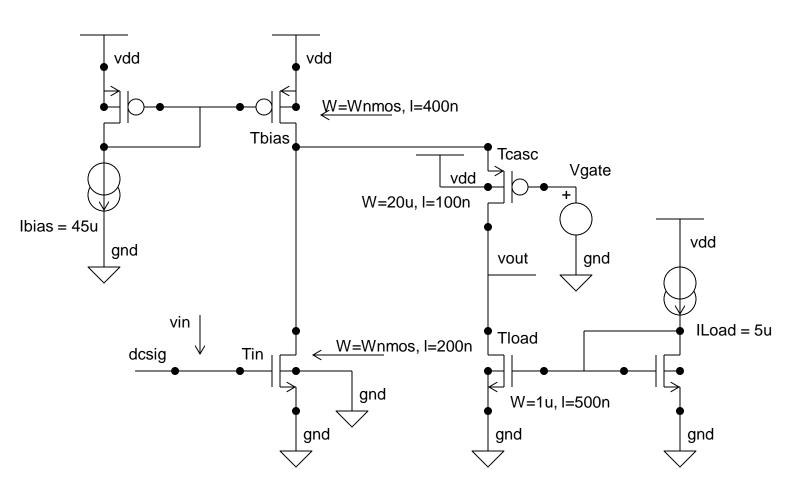

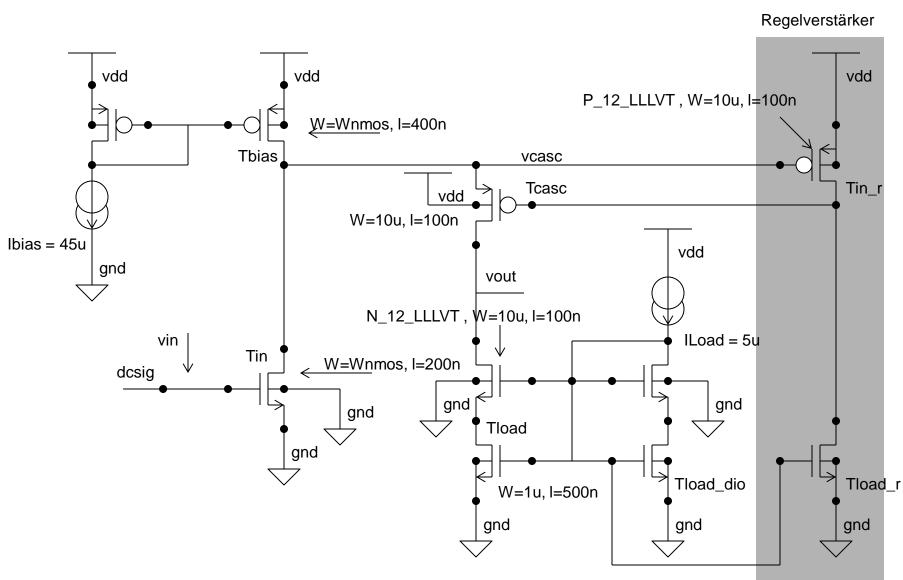

- Aufgabe 8: Entwerfen wir den Verstärker mit gefalteter Kaskode (s. Abbildung)

- Wählen wir den Biasstrom Ibias etwa 45uA und den Biasstrom Iload 5uA

- Ids Strom des NMOS Transistors Tload (Last-Element) ist dadurch etwa 10x kleiner als Ids des Eingangstransistors Tin.

- Wählen wir W/L vom Tload etwa 20 mal kleiner als W/L vom Tin. (W/L\_load = 1u / 500n) In dem Fall ist Vdssat des Last-Transistors Tload etwa 150mV.

- Die Kaskode Tcasc soll möglichst große gm haben, damit die sich ihre Gate-Source Spannung so wenig wie möglich ändert -> W/L = 10u/100n.

- Setzen wir das Gate-Potential von Tcasc (Vgate) auf:

- VDD Vdssat\_Tbias Vdssat\_Tcasc Vth\_casc = 1.2V 200mV 50mV 0.45V = 500mV.

- Machen wir die Hilfsschaltung mit der Gegenkopplung zwischen vin und vout und pr

üfen wir ob alle Transistoren in Sättigung sind

- Aufgabe: Simulieren wir die DC-Kennlinie vom Verstärker mit gefalteter Kaskode und machen ein Screenshot

- Frage: Wie groß ist ungefähr die DC Verstärkung im Arbeitspunkt vout = vin ~ 500mV

- Frage: In welchem Ausgangs-Spannungsreich sind alle Transistoren in Sättigung

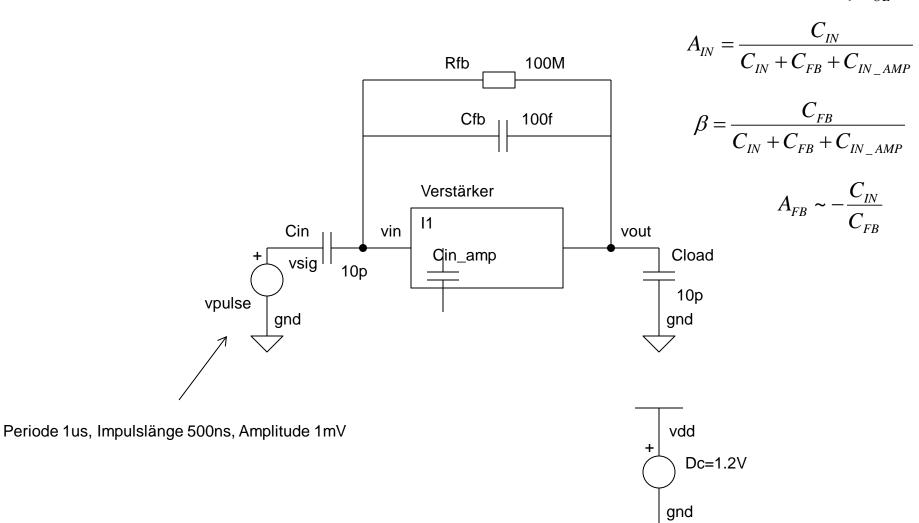

- Aufgabe 9: Erzeugen wir einen neuen, leeren, Schaltplan für den Verstärker mit gefalteter Kaskode und kopieren wir die Schaltung aus der vorherigen Aufgabe

- Machen wir den Input Pin "vin" und den Output Pin "vout" (Create Pin Befehl)

- Erzeugen wir ein Symbol aus dem Schaltplan (Create Cellview -> From Cellview)

- Der Verstärker hat eine hohe Spannungsverstärkung sie ist, jedoch, von den Prozessparameter wie gm und rds anhängig

- Wir werden in dieser Aufgabe eine kapazitive Gegenkopplung verwenden um die Verstärkung von Transistorparameter unabhängig zu machen - unser ziel ist die Verstärkung mit Gegenkopplung von 100

- Erzeugen nur noch einen Schaltplan für die Simulation des Verstärkers mit Gegenkopplung (s. Abbildung)

- Dieser Schaltplan enthält den Verstärker mit gefalteter Kaskode als Symbol (Create Instance), die Rückkopplung, eine Last-Kapazität und eine Impuls-Spannungsquelle

- Beachten wir: für sehr höhe Leerlaufverstärkung erwarten wir Afb = Cin/Cfb = -100. Rfb soll hoch genug sein um die AC-Antwort nicht zu beeinflussen, und niedrig genug sein um Vout = Vin im Arbeitspunkt zu gewährleisten.

- **Aufgabe:** Simulieren wir die Sprungantwort (0, 2us) zuerst ohne Lastkapazität am Ausgang. Machen wir ein Screenshot. Wie groß ist die Verstärkung vout/vsig?, wie groß ist die Anstiegszeit 5%-95% ungefähr?

- Frage: Wie groß ist die Leerlaufverstärkung Aol = vout/vin? Wie groß Beta A\_ol?

- **Frage:** Um wie viel % ist die Verstärkung niedriger als die gewünschte Verstärkung Cin/Cfb = 100.

- Nach dem Sprungantwort entlädt sich der Kondensator Cfb durch Rfb langsam, das kann zu Fehlern führen, z.B. wenn die Ausgangsspannung in einem digitalen System zu spät abgetastet wird

$$A_{FB} = \frac{A_{IN}A_{OL}}{1 + \beta A_{OL}}$$

- Aufgabe10

- Erweitern wir die Schaltung des Verstärkers durch eine aktive Regelung der Kaskodenspannung (geregelte Kaskode) und kaskodieren wir den NMOS Stromspiegel (s. Abbildung)

- Für die Kaskoden im NMOS Spiegel verwenden wir die Transistoren mit niedriger Schwelle wie in Aufgabe 3. Dadurch sparen wir uns eine getrennte Gate Spannung

- Der Eingangstransistor des Regelverstärkers (Tin\_r) ist ein PMOS mit niedriger Schwelle dadurch erreichen wir ein passendes vcasc Potential von etwa VDD – 300mV.

- Für die Gate-Spannung der Stromquelle im Regelverstärker (Tload\_r) nehmen wir die Spannung von Iload "Diode" Tload\_dio – dadurch sparen wir uns einen getrennten Referenzstrom

- Aufgabe: Simulieren wir die Sprungantwort ohne Lastkapazität am Ausgang und bestimmen wir die Verstärkung Afb = vout/vsig und die Leerlaufverstärkung Aol = vout/vin

- Wir erwarten etwa um Faktor gm Rds ~ 10 höhere Verstärkung als ohne Kaskoden-Regelung und mit dem einfachen Stromspiegel

- Aufgabe11

- Simulieren wir das Rauschen am Ausgang des Verstärkers

- Aktivieren wir AC Noise Analyse, der Ausgangsspannung ist vout, der Referenzknoten gnd.

- Eine Eingangsquelle muss für die Berechnung vom Eingangsrauschen (Input-Referred Noise) gewählt werden – das kann die Eingangs- Impulsquelle sein

- Es wird zuerst die Rauschleistung im Frequenzdomain simulieret. Uns interessiert hauptsächlich das Quadratwurzel vom Integral der Rauschleistung für alle Frequenzen. Dieser Wert ist equivalent zur Standardabweichung (RMS-Wert) der Rausch-Spannung am Ausgang. Um das Integral zu berechnen verwenden wir Print -> Noise Summary. Das Tool zeigt eine Liste von Bauteilen sortiert nach ihrem Rauschbeitrag. Mithilfe dieser Liste können wir die größten Rauschquellen identifizieren und die Schaltung optimieren

- Frage: Wie groß ist das Rauschen (RMS) am Ausgang

- Frage: Wir groß ist Input Referred Noise, definiert als das Rauschen vom vout dividiert durch die DC-Verstärkung

- Aufgabe12

- Simulieren wir den Verstärker mit Cload = 10pF

- Für die Schaltung mit einem einstufigen Verstärker (wie unserem) ist die Zeitkonstante mit Gegenkopplung etwa Cload/(Beta \* gm\_in). Gm\_in ist ungefähr 600uSi (Überprüfen Sie gm-Wert mit dem "Calculator")

- Beta ist ungefähr Cfb/(Cfb+Cin) ~ 0.01.

- Wir erwarten also eine Zeitkonstante von 1.66 us.

- Für eine Impulslänge von 1us, erreicht die Ausgangsspannung nur ~30% des Endwertes.

- Wir können die Schaltung durch einen Trick schneller machen:

- Multiplizieren wir die Symbole des Verstärkers indem wir als Instanz-Name statt Ix Ix<0:49> schreiben.

- Auf diese Weise haben wir 50 Verstärkern in parallel. Der Trick besteht darin, dass wir dadurch gesamt gm\_in erhöhen (50 Eingangstransistoren in parallel haben 50-fache gm), gesamt Aol bleibt dabei gleich (mehrere Verstärker in parallel haben die gleiche Verstärkung als ein einzelner).

- Wir erwarten also eine Anstiegszeit von nur 1.66us/50 = 34ns, unter Annahme dass gm\_in 50x größer und Beta unverändert werden

- Aufgabe: Simulieren wir die Schaltung mit 50 Verstärkern in parallel, speichern wir das Screenshot

- Aufgabe11 (2):

- Bemerkung: Die Verwendung von vielen Verstärkern in parallel ist eine gute Vorgehensweise für die Optimierung von Transistorparameter. Die Spannungen an Transistorelektroden bleiben unverändert und die Bedingungen für Sättigung bleiben erfüllt

- Die Schaltung mit 50 Verstärkern ist schneller, hat aber als Nachteil einen 50-fach höheren Stromverbrauch und eine höhere Layout-Fläche

- Falls wir viele Verstärkern in parallel haben, wird die Eingangskapazität des Verstärkers Cin\_amp groß und oft vergleichbar mit Cin. Die Formel für Beta muss dann wie folgend korrigiert werden:

- Beta = Cfb/(Cfb + Cin + Cin\_amp).

- In unserem Fall (50 Verstärkern in parallel) ist Cin\_amp ~ 1pF ~ Cin. Deshalb ist Beta nur etwa die Hälfte vom Wert mit einem Verstärker und die Zeitkonstante ist länger als die erwarteten 34ns

- In 65nm Technologie ist der Tunnelstrom durchs Gate nicht vernachlässigbar. Vergleichen wir vin und vout Werte im Abreitpunkt. Wir erklären Sie die Differenz?

- Aufgabe10 (3)

- Simulieren wir das Rauschen am Ausgang des Verstärkers

- Frage: Wie groß ist das Rauschen (RMS) am Ausgang

- Frage: Wir groß ist Input Referred Noise, definiert als das Rauschen vom vout dividiert durch die DC-Verstärkung